Ini laporan ngeposting lewat blog yang ke 3 kalinya. Saya masih tetap semangat untuk ngerjain tugas, entah nilainya berapa yang penting ngumpulin tepat waktu!hehehe

Aku nggak suka kalo mesti nunda nunda pekerjaan, soalnya ntar kita sendiri yang bakal repot apalagi mesti begadang buat ngerjain tugas!

bener nggak??????

Langsung ja ya ke laporan yang ke 3…..

GERBANG PEMBANGUN UNIVERSAL

Gerbang NAND mempunyai dua atau lebih sinyal input, serta satu buah sinyal keluaran. Keluaran NAND gate akan bernilai 1, apabila satu atau lebih dari sinyal input berlogik 0,dan keluaran NAND gate akan bernilai 0 apabila semua sinyal inputnya berada pada logik 1. Gerbang NAND dapat digunakan untuk membangun gerbang-gerbang dasar yang lain sehingga disebut sebagai gerbang pembangun universal.

Rangkaian Percobaan

Rangkaian Percobaan Gerbang AND

Diagram Logika gerbang AND

Skema penkabelan gerbang AND

Rangkaian percobaan Gerbang AND

Tabel kebenaran Gerbang AND

Penjelasan :

Keluaran gerbang AND akan berlogika 1 jika semua masukkannya 1. notasi Boole untuk gerbang AND adalah tanda .(kali). A yang di AND kan dengan B dinotasikan A.B.

Rangkaian Percobaan Gerbang OR

Diagram Logika gerbang OR

Skema penkabelan gerbang OR

Rangkaian percobaan Gerbang OR

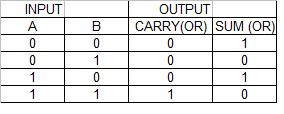

Tabel Gerbang kebenaran Gerbang OR

Penjelasan :

Keluaran gerbang OR akan berlogika 1 jika semua masukkannya 1. notasi Boole untuk gerbang OR adalah tanda + (plus). A yang di OR kan dengan B dinotasikan A+B.

Rangkaian Percobaan Gerbang NOR

Diagram Logika gerbang NOR

Rangkaian percobaan Gerbang NOR

Tabel Gerbang kebenaran Gerbang NOR

Penjelasan :

Gerbang NOR (NOT OR) merupakan gabungan dari gerbang OR dan NOT . keluaran gerbang ini berkebalikan dari keluaran gerbang OR. Gerbang NOR dapat dibentuk dengan menambahkan gerbang NOT dibagian keluaran gerbang OR. Tanda lingkaran kecil dikeluaran gerbang NOR menandakan bahwa telah digabungkan gerbang NOT dan gerbang aslinya.

Notasi Boole untuk gerbang NOR adalah tanda + diikuti dengan pemberian garis diatasnya. A yang di NOR kan dengan B dinotasikan A+B.

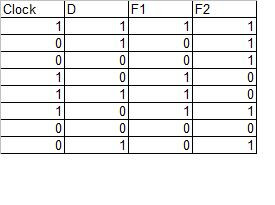

Rangkaian Percobaan Gerbang EX-OR

Diagram Logika gerbang EX-OR

Skema penkabelan gerbang EX-OR

Rangkaian percobaan Gerbang EX-OR

Tabel Gerbang kebenaran Gerbang EX-OR

Penjelasan :

Gerbang EX-OR atau x-OR mempunyai ciri khusus yaitu keluaran gerbang ini akan berlogika 1 jika logika masukan gerbang ini berbeda dan berlogika 0 jika logika masukan gerbang ini sama. Notasi Boole untuk gerbang EX-OR adalah tanda

+ ..A yang di-EX-OR-kan dengan B dinotasikan A+ B. Gerbang EX-OR dapat dibentuk dari beberapa gerbang dasar,yaitu dua buah gerbang NOT,dua buah gerbang AND dan satu gerbang OR.

TUGAS

5. Rangkaian Percobaan Gerbang EX-NOR

Diagram Logika gerbang EX-NOR

Skema penkabelan gerbang EX-NOR

Rangkaian percobaan Gerbang EX-NOR

Tabel Gerbang kebenaran Gerbang EX-NOR

Penjelasan :

Gerbang EX-NOR atau X-OR merupakan gabungan dari gerbang EX-OR yang keluarannya diNOT kan sehingga keluaran gerbang ini berkebalikan dengan kelu7aran gerbang EX-OR. Keluaran gerbang ini akan berlogka 1 jika logika masukan gerbang ini sama dan berlogika 0 jika logika masukan gerbang ini berbeda. Notasi Boole untuk gerbang EX-NOR adalah tanda + diikuti dengan pemberian garis diatasnya. A yang diEX-NOR kan dengan B dinota sikan A + B, . Gerbang EX-NOR dapat dibentuk dari beberapa gerbang dasar,yaitu dua buah gerbang NOT,dua buah gerbang AND dan satu gerbang OR.

Label: GPU